Prozessorarchitektur

Z80 Interrupt-Logik

aus Wikipedia, der freien Enzyklopädie

Inhaltsverzeichnis |

[Bearbeiten] Z80 Interrupt Logik

Mikroprozessoren kommunizieren mit externen Geräten über sogenannte Peripheriebausteine um beispielsweise Daten von einem Modem zu empfangen. Damit der Prozessor schnell auf externe Ereignisse, z.B. der Empfang eines Zeichens reagieren kann, sendet das Peripheriegerät eine Unterbrechnungsanforderung (Interrupt) an den Prozessor, der sein normales Programm unterbricht, in eine Interrupt-Service-Routine (ISR) verzweigt und nach Verarbeitung des Zeichens im normalen Programmfluss fortfährt. Um einen Interrupt an den Prozessor zu übergeben, werden meist spezielle Bausteine, sogenannte Interrupt-Controller benötigt. An diese Controller können mehrere Peripheriebausteine angeschlossen werden, im Ur-PC von IBM beispielsweise acht Stück. Sollen mehr als acht externe Geräte angeschlossen werden, wird ein weiterer Controller benötigt, welcher zu aufwändigen Design-Änderungen führt.

[Bearbeiten] Das Interrupt-Konzept des Z80

Zilog baute die Interrupt-Steuerung des Z80-Prozessors daher völlig anders auf. Der Z80 brauchte gar keinen Interrupt-Controller, konnte aber trotzdem bis zu 128 externe Interrupt-Quellen bedienen - bei einer zugleich sehr einfachen Software-Struktur. Damit der Z80 die richtige ISR bedienen kann, besitzt jeder Peripheriebaustein ein 8-Bit breites Register, das zusammen mit einem internen CPU-Register auf eine Interrupt-Vektor-Tabelle im Speicher zeigt, die wiederum die Einsprungadressen der ISR's enthält. Da das unterste Bit des Interrupt-Registers immer 0 sein muss, ergeben sich somit maximal 128 Einträge in der Interrupt-Vektor-Tabelle.

[Bearbeiten] Ablauf einer Unterbrechnungsanforderung

- Das Peripheriegerät aktiviert an der CPU ein Interrupt-Request-Signal (IRQ)

- Die CPU bestätigt die Interrupt-Anforderung.

- Das Peripheriegerät legt daraufhin den Inhalt des Interrupt-Registers auf den Datenbus.

- Die CPU unterbricht das laufende Programm, liest die Adresse, holt sich aus der Interrupt-Vektor-Tabelle die Adresse des zugehörigen Programmcodes ISR und führt diesen aus.

Nach Abarbeitung der Interrupt-Service-Routine führt die CPU das unterbrochene Programm fort.

[Bearbeiten] Konfliktmanagement

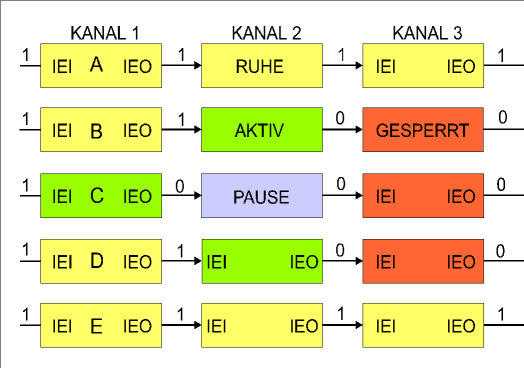

Da mehrere externe Ereignisse gleichzeitig eintreffen und außerdem auch wichtige Ereignisse die ISR's von unwichtigeren Ereignissen unterbrechen können, braucht man eine Konflikt- oder Prioritätssteuerung. Wie bei den Vektoren sind auch hier die Peripheriebausteine dafür verantwortlich. Jeder Baustein besitzt je einen Eingang (Interrupt Enable Input, IEI) und einen Ausgang (Interrupt Enable Output, IEO). Alle beteiligten Bausteine sind in Kette geschaltet, der IEO ist mit dem IEI des jeweils nächsten verbunden. Der IEI des ersten Gliedes liegt fest auf Logisch 1. Es gilt:

- Ein Interrupt wird nur ausgelöst, wenn IEI logisch 1 ist.

- Ist ein Interrupt aktiv, so wird IEO logisch 0, was zur Folge hat, dass alle folgenden Glieder der Kette gesperrt sind.

- Daraus ergibt sich, dass das erste Glied der Kette immer die höchste Priorität hat.

Das Bild soll dies näher erläutern:

- A: Ruhezustand, alle Bausteine können einen Interrupt auslösen.

- B: Kanal 2 hat Interrupt ausgelöst, sperrt Kanal 3

- C: Kanal 1 löst Interrupt aus, unterbricht die ISR von Kanal 2

- D: Interrupt von Kanal 1 ist beendet, ISR von Kanal 2 geht weiter.

- E: Interrupt von Kanal 2 ist beendet, es geht im normalen Programmfluss weiter.

Damit die Peripheriebausteine wissen, wann sie ihr IEO wieder freigeben dürfen, lauschen sie mit, welchen Programmcode die CPU gerade ausführt. Jede ISR endet mit dem Befehl RETI (ED 4D), was der externe Baustein erkennt und daraufhin sein IEO freigibt.

[Bearbeiten] Die Trickkiste

Oft ist es wünschenswert, die Interrupt-Prioritäten vom Programm aus zu ändern, was aber wegen der starren Hardware-Verdrahtung nicht möglich ist. Mit einigen Kniffen geht es trotzdem, dass beispielsweise Kanal 3 die ISR von Kanal 1 unterbricht.

Standard-ISR:

Kanal2:

PUSH AF ;Sichern der Register

PUSH BC

PUSH DE

PUSH HL

EI ;neue Interrupts gleich wieder erlauben

...

LD HL,irgendwas ;Der Programmcode

...

POP HL

POP DE

POP BC

POP AF ;zurückholen der Register

RETI ;Ende der ISR

Kanal 1 könnte die ISR von Kanal 2 unterbrechen, nicht aber Kanal 3, da dieser per Hardware gesperrt ist. Um die Hardware zu überlisten, wird folgendes Programmfragment benutzt:

Tricky ISR:

Main:

LD DE,wasauchimmer

ADD HL,DE

...

LD A,1 ;<--- Hier wird der Interrupt wirksam,

;Die Adresse Main_R wird als Ruecksprungadresse auf den

;Stack gelegt.

Main_R:

LD B,2

....

;Interrupt-Service-Routine fuer Kanal2

Kanal2:

CALL TRICKY_SAVE ;Unterprogramm

Kanal2_R:

...

LD HL,irgendwas

...

RET

TRICKY_SAVE:

EX (SP),HL ;Rücksprung-Adresse nach HL holen

PUSH AF ;Register sichern

PUSH BC

PUSH DE ;Stack: MAIN, HL, AF, BC, DE

;HL: Kanal2_R

LD DE,CONTINUE ;Adresse von Programmcode CONTINUE

PUSH DE ;als Ruecksprungadresse auf Stack legen

EI

RETI ;Programm wird durch den RETI-Befehl an der

;manipulierten Rücksprungadresse CONTINUE

;fortgesetzt. Das Peripheriegerät erkennt

;die RETI-Instruktion, betrachtet damit "seine"

;ISR als beendet und gibt den Interrupt wieder

;frei.

CONTINUE:

CALL HL_JP ;Der Programmcode wird an der im HL-Register

;gespeicherten Adresse (=Kanal2_R) fortgesetzt

POP DE ;Register zurueckholen

POP BC

POP AF

POP HL

RET ;normales return reicht hier aus, da RETI bereits

;ausgefuehrt wurde.

HL_JP:

JP (HL)

Jedes Peripheriegerät kann damit jederzeit einen Interrupt auslösen, die Prioritätssteuerung kann per Software erfolgen.

[Bearbeiten] Weblinks

Kategorien

Hardware

Bussystem

CPU-Sockel

Chipsatz

Computer

Gehäuse

Grafikchip

Hardware (Produkt)

Hardwarehersteller

Internet (Hardware)

Mikrocontroller

Mikroprozessor

Netzwerkgerät

Programmierbare Logik

Schnittstelle (Hardware)

Soundchip

Speicherkarte

Speicherlaufwerk

Speichermedium

Speichermodul

Standard (Hardware)

Steckkarte

Urheberrecht

Text und Bilder der Lexikonartikel stammen aus der freien Enzyklopädie Wikipedia und stehen unter der GNU Free Documentation License.

Text und Bilder der Lexikonartikel stammen aus der freien Enzyklopädie Wikipedia und stehen unter der GNU Free Documentation License.