Schnittstelle (Hardware)

Joint Test Action Group

aus Wikipedia, der freien Enzyklopädie

JTAG steht für "Joint Test Action Group" und bezeichnet normalerweise den IEEE-Standard 1149.1, der ein Verfahren zum Testen und Debuggen von elektronischer Hardware direkt in der Schaltung beschreibt.

Der JTAG-Standard entstand durch einen Zusammenschluss von Halbleiterherstellern im Jahr 1985/86. Es wurde ein Standard erarbeitet, der in der Norm IEEE 1149.1-1990 festgehalten ist. Das Verfahren ist auch unter dem Namen Boundary Scan Test bekannt.

Der Zweck des Verfahrens ist, Integrierte Schaltungen (ICs) auf Funktion zu testen, während sie sich bereits in ihrer Arbeitsumgebung befinden, beispielsweise verlötet auf einer Platine. Dazu besitzt ein JTAG-fähiges IC bestimmte JTAG-Komponenten, die im Normalbetrieb vollkommen abgetrennt sind und somit die Funktion des Bauteils nicht stören. Erst durch Aktivierung der JTAG-Funktion an einem bestimmten Pin, dem Test Mode Select Input, wird die Kontrolle bestimmter Ein- und Ausgänge an JTAG übergeben.

Ende der 1970er Jahre war der Integrationsgrad der Mikroelektronik soweit gestiegen (man denke an Intel 4004, Intel 8008, Zilog Z80 etc.), dass ICs mit dutzenden Flipflops bzw. Registern in einem IC arbeiteten.

Da in ICs stets asynchrone Schaltungsteile implementiert werden, entstand ein Testproblem. Die inneren Zustände asynchroner Flipflops sind bei einem IC nicht mehr zugänglich. Man denke zum Beispiel an einen IC einer 32 kHz Quarzuhr: hier sind mehrere Flipflops in Reihe geschaltet, die von außen eigentlich nicht beobachtbar sind.

Es entstand die Forderung (zunächst der IC-Hersteller selbst), daß zum Test der Struktur eines komplexen IC dessen Gatter und Leitungen steuerbar; zum Test der Funktion die Zustände (aller Register und Flipflops) beobachtbar zu sein haben.

Eichelberger (siehe unten) veröffentlichte 1977 einen als Scan-Path bezeichneten Lösungsansatz, bei dem jedes Flipflop im IC einen zusätzlichen Multiplexer (Transfergate) am Eingang erhält. Auf diese Weise können nun alle Flipflops des IC wahlweise zu einem langen Schieberegister zusammengeschaltet werden, über welches jeder Zustand jedes Flipflops von außen beobachtbar und steuerbar wird.

Inhaltsverzeichnis |

[Bearbeiten] Funktionsweise

Ähnlich einer speicherprogrammierbaren Steuerung können dann alle Ein- und Ausgänge den Spannungspegel von HI auf LOW und umgekehrt ändern. Die Programmierung über JTAG erfolgt seriell. Das heißt, dass je nach Anzahl der zu steuernden Ein- und Ausgänge, in ein Schieberegister des Bauteils nacheinander eine Folge von HI (1) und LOW (0) Spannungspegeln eingeschoben wird. Erst wenn sämtliche Bits des Schieberegisters den gewünschten Wert besitzen, werden die Spannungspegel an den Ausgängen ausgegeben.

[Bearbeiten] Leitungen

Im allgemeinen wird von der JTAG-Schnittstelle oder dem JTAG-Port gesprochen. Dieser besteht aus fünf Steuerleitungen:

- Test Data Input (TDI) (positive Flanke)

- Test Data Output (TDO) (negative Flanke)

- Test Clock (TCK) (positive Flanke)

- Test Mode Select Input (TMS)

- Test Reset (TRST) (optional)

[Bearbeiten] Verdrahtung in der Gesamtschaltung

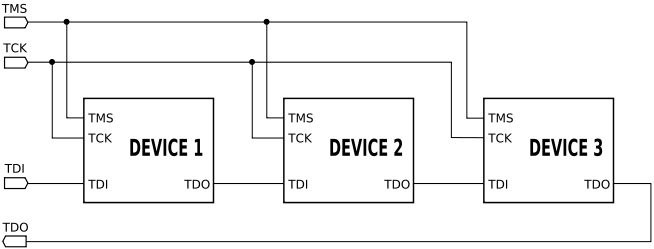

An eine JTAG-Schnittstelle können mehrere Integrierte Schaltungen angeschlossen werden, wie im folgenden Bild zu sehen. Im Englischen spricht man von einer „JTAG chain“.

[Bearbeiten] Datenübertragung

Bei der TCK-Leitung handelt es sich um die Taktleitung für die synchronen Flipflops der internen Schieberegister und um die Taktleitung des internen Zustandsautomaten.

Intern verfügt ein IC mit JTAG-Port über mindestens ein Schieberegister. Bei einer Schiebeoperation wird dabei der TDI-Eingang in das vorderste Bit des Schieberegisters „hineingeschoben“, das hinterste Bit des Schieberegisters wird zum TDO-Ausgang „hinausgeschoben“. Sind mehrere ICs in einer „JTAG-Chain“ hintereinantergeschaltet, werden Informationen, die für ein bestimmtes IC gedacht sind, durch die Schieberegister der vorherigen hindurchgeschoben.

Die TMS-Leitung steuert den internen Zustandsautomaten, der wiederum die Schieberegister ansteuert. Das folgende Bild zeigt diesen Zustandsautomaten. Die 0 bzw. 1 an einem Zustandsübergang gibt dabei den Wert der TMS-Leitung an. Für Fälle, in denen kein Zustandsübergang gezeichnet ist (z.B. Zustand="Bit shiften" und TMS=0) erfolgt kein Zustandswechsel (im Fall von "Bit shiften" wird ein weiteres Bit geshiftet). Ist der aktuelle Zustand "Bit shiften", so werden Datenbits (TDI, TDO) geschoben (sowohl beim Verbleib im Zustand - TMS=0 - als auch beim Verlassen des Zustandes - TMS=1, nicht jedoch bereits beim Zustandsübergang von einem anderen Zustand nach "Bit shiften").

Damit wird folgende Sprache (in EBNF) beschrieben:

Start ::= 1* 0 A

A ::= [W]1 ( R Start | L [S]1 (W1S1)* [W1] X A )

wobei

W ::= 0+ "Warten"

R ::= 11 "Reset"

L ::= 0 "DR-Register ins SR laden" | 10 "IR-Register ins SR laden"

S ::= 0ⁿ "SR um n≥1 Bit Shiften"

X ::= 1 "SR zurückschreiben"

[Bearbeiten] Register

Ein IC mit JTAG-Port verfügt über mehrere Register. Diese können entweder als eigenständige Schieberegister ausgeführt sein oder der Zugriff auf mehrere Register kann über ein gemeinsames Schieberegister erfolgen.

[Bearbeiten] Das "Instruction Register" (IR)

Wenn eine Schiebeoperation durch die Datenregister (DR, siehe unten) erfolgt, so gibt der Wert des "Instruction Registers" (IR) an, durch welches der Datenregister die Schiebeoperation erfolgt. Aufgrund der Verschaltung der Schieberegister können die Instruction Register aller Schaltkreise in einer "JTAG chain" nur gemeinsam geschrieben werden.

Das IR ist bei einigen ICs 4 Bit (z.B. ARM, Maxim/Dallas DS4550, Renesas SH-Microcontroller), bei anderen 5 Bit (z.B. Freescale MPC5554) oder auch 8 Bit (z.B. Infineon C166) breit.

Bestimmte Werte des IR können vom IC bei Beendigung der Schiebeoperation als Kommando interpretiert werden.

[Bearbeiten] Das Bypass-Register

Bei diesem Daten-Register handelt es sich um ein Dummy-Schieberegister mit einem Bit Breite. Hintergrund dieses Registers ist, dass die Datenregister (DR) aller ICs wie beim IR nur gleichzeitig gelesen und beschrieben werden können.

Soll nur das Datenregister eines einzelnen ICs in der "JTAG chain" gelesen oder geschrieben werden, so wird in die IRs aller anderen ICs der Wert "Bypass-Register auswählen" geladen, so dass dieses Register ausgewählt wird. Dadurch wirken diese ICs beim Schieben durch die DRs lediglich wie zwei parasitäre Schieberegister vor und hinter dem DR des ICs, das eigentlich beschrieben werden soll.

[Bearbeiten] Das IDCODE-Register

Beim Beginn einer Schiebeoperation durch dieses Datenregister (DR) wird eine IC-Kennung (Hersteller und Produkttyp) in das Schieberegister geladen, die zur Identifizierung des ICs dient.

[Bearbeiten] Das Boundary-Scan-Register

Die Bits dieses Datenregisters (DR) repräsentieren die Pins des IC. Die genaue Bedeutung ist herstellerabhängig.

[Bearbeiten] Sonstige Register

Wird eine JTAG-Schnittstelle z.B. zum Debuggen verwendet, so verfügt das IC über spezielle, herstellerspezifische Debugging-Register, beispielsweise im Fall von ARMv5 drei spezielle Register, die als Datenregister (DR) angesprochen werden.

[Bearbeiten] Weitere Anwendungen

Inzwischen wird JTAG vermehrt auch zur Konfiguration von FPGAs und CPLDs sowie zum Programmieren und zum Debuggen von Mikrocontrollern verwendet. Parallel programmierbare Speicher wie zum Beispiel Flashspeicher, die direkt an ein IC mit JTAG-Port angeschlossen sind, können deshalb im eingebauten Zustand umprogrammiert werden, weil das IC für den Speicherchip ein Programmiergerät emulieren kann. Um den JTAG-Port eines ICs nutzen zu können, ist es notwendig, seinen Aufbau genau zu kennen. Dieser wird in einer vom Hersteller bereitgestellten BSDL-Datei (Boundary Scan Description Language) beschrieben.

[Bearbeiten] Siehe auch

- Boundary Scan

- Eichelberger, u.a.: A logic Design Structure for LSI Testability. Proc. 14th DAC, June 1977, S.463-468

[Bearbeiten] Weblinks

- JTAG Technologies: Standards + Technische Infos

- JTAG Tutorial and Boundary-Scan Applications

- JTAG-FAQ (engl.)

- Free JTAG Resources

- Overview of JTAG technology - Design for Testability (DFT) Guidelines, BGA, ISP; Chain Integrity, Connection & Functional Testing

- Brief technical guide to JTAG Boundary Scan - An overview of how JTAG is implemented. Signals, TAP controller, Registers, Instructions.

- Mehr über intelligente Lösungen und Integrationsmöglichkeiten von JTAG/Boundary Scan

Kategorien

Hardware

Bussystem

CPU-Sockel

Chipsatz

Computer

Gehäuse

Grafikchip

Hardware (Produkt)

Hardwarehersteller

Internet (Hardware)

Mikrocontroller

Mikroprozessor

Netzwerkgerät

Programmierbare Logik

Schnittstelle (Hardware)

Soundchip

Speicherkarte

Speicherlaufwerk

Speichermedium

Speichermodul

Standard (Hardware)

Steckkarte

Urheberrecht

Text und Bilder der Lexikonartikel stammen aus der freien Enzyklopädie Wikipedia und stehen unter der GNU Free Documentation License.

Text und Bilder der Lexikonartikel stammen aus der freien Enzyklopädie Wikipedia und stehen unter der GNU Free Documentation License.