Prozessorarchitektur

Adressrechner (Maschinenbefehl)

aus Wikipedia, der freien Enzyklopädie

Prozessoren lassen sich durch eine Vielzahl von Eigenschatften unterscheiden. Eine der elementarsten Eigenschaften sind die Anzahl der Adressbefehle im Maschinenbefehl. Diese Eigenschaften sind ausschlaggebend für die Rechnerstruktur und den Prozessortyp.

Inhaltsverzeichnis |

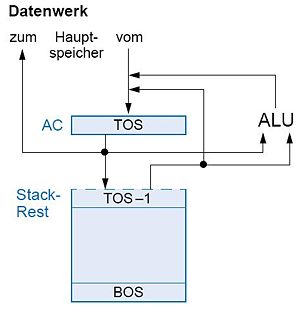

[Bearbeiten] 0-Adressbefehle / Stackrechner

Die Befehle der ALU sind 0-Adressbefehle mit eingeschlossener/impliziter Adressierung, das heißt das die ALU-Operationen direkt aus dem Top Of Stack bzw. (Top Of Stack - 1) lesen und schreiben. Beim Schreiben werden auf das TOS werden die darunterliegenden Stackinhalte nach unten verschoben und beim Lesen werden die darunterliegenden Stackinhalt nach "oben angehoben".

Jedoch erfolgen alle Speicherzugriff über PUSH Var und POP Var , sprich 1-Adressbefehle.

[Bearbeiten] Beispiel

Berechnung

Assemblercode

PUSH X PUSH Y ADD PUSH C MULT POP A

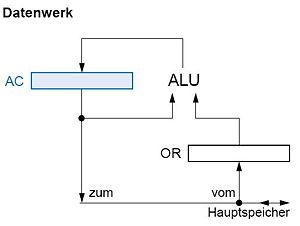

[Bearbeiten] 1-Adressbefehle / Akkumulatorrechner

Die Befehle der ALU sind 1-Adressbefehle mit eingeschlossener/impliziter Adressierung als 1.Quelle ( und Ziel ) und mit Speicherzugriff als 2.Quelle. Die Speicherzugriffe erfolgen auch über 1-Adressbefehle, als Beispiel an dem VIP LDA X (Lade X in den Akkumulator-Register) und STA X (Speichere in Inhalt des Akkumulator-Register in X)

[Bearbeiten] Beispiel

Berechnung

Assemblercode(am Beispiel des VIP)

LDA X ADD Y MULT C STA A

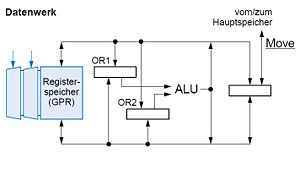

[Bearbeiten] 2-Adressbefehle / typisch CISC-Rechner

Das Akkumulator-Register ist durch ein allgemeinen Registerspeicher ersetzt worden, im Bild der GPR. Die Benutzung der Speicherzellen dient beispielsweise als Indexregister,Datenregister, Adressregister usw.

Transportbefehle und Befehle in der ALU sind 2-Adressbefehle mit einer Registeradresse als 1.Quelle und Ziel und einer Register-/Speicheradresse als zweite Quelle.

[Bearbeiten] Beispiel

Berechnung

Assemblercode

MOVE.W R1,X ADD.W R1,Y MULT.W R1,C MOVE.W A,R1

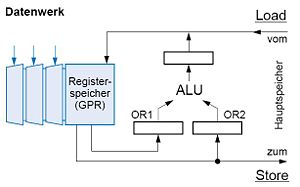

[Bearbeiten] 3-Adressbefehle / typisch RISC-Rechner

Das Akkumulator-Register ist durch ein allgemeinen Registerspeicher ersetzt worden, im Bild der GPR. Dieser Registerspeicher erlaubt eine 3 Port Speicher, das heißt zwei Lese- und einen Schreibzugriff zeitgleich, somit wird eine Unterstützung der Fließbandverarbeitung gewährleistet.

[Bearbeiten] Beispiel

Berechnung

Assemblercode

LD.W r1, 0(r_x) LD.W r2, 0(r_y) ADD r1, r2, r1 LD.W r2, 0(r_c) MULT r2, r2, r1 ST.W r2, 0(r_a)

[Bearbeiten] Literatur

- Thomas Flik: Mikroprozessortechnik und Rechnerstrukturen., 7.Auflage Springer Berlin 2005. ISBN 3-540-22270-7

- Andrew S. Tannebaum: Computerarchitektur. Strukturen - Konzepte - Grundlagen, 5.Auflage München 2005 . ISBN 3-827-371511

- Matthias Menge : Moderne Prozessorarchitekturen. Prinzipien und ihre Realisierungen: Prinzipien Und Ihre Realisierungen , 1.Auflage Springer Berlin 2005 . ISBN 3-540-24390-9

Kategorien

Hardware

Bussystem

CPU-Sockel

Chipsatz

Computer

Gehäuse

Grafikchip

Hardware (Produkt)

Hardwarehersteller

Internet (Hardware)

Mikrocontroller

Mikroprozessor

Netzwerkgerät

Programmierbare Logik

Schnittstelle (Hardware)

Soundchip

Speicherkarte

Speicherlaufwerk

Speichermedium

Speichermodul

Standard (Hardware)

Steckkarte

Urheberrecht

Text und Bilder der Lexikonartikel stammen aus der freien Enzyklopädie Wikipedia und stehen unter der GNU Free Documentation License.

Text und Bilder der Lexikonartikel stammen aus der freien Enzyklopädie Wikipedia und stehen unter der GNU Free Documentation License.